#### ACTIVE BALUN BASED ON OTA DEVICE

**SITTAN UDOMSOM**

MASTER OF ENGINEERING

IN

COMPUTER ENGINEERING

SCHOOL OF INFORMATION TECHNOLOGY

MAE FAH LUANG UNIVERSITY

2012

©COPYRIGHT BY MAE FAH LUANG UNIVERSITY

#### ACTIVE BALUN BASED ON OTA DEVICE

SITTAN UDOMSOM

# THIS THESIS IS A PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF ENGINEERING IN COMPUTER ENGINEERING

SCHOOL OF INFORMATION TECHNOLOGY

MAE FAH LUANG UNIVERSITY

2012

©COPYRIGHT BY MAE FAH LUANG UNIVERSITY

#### ACTIVE BALUN BASED ON OTA DEVICE

#### SITTAN UDOMSOM

# THIS THESIS HAS BEEN APPROVED TO BE A PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF ENGINEERING

IN

COMPUTER ENGINEERING

2012

#### THESIS COMMITTEE

| 5 mra                           | CHAIRPERSON       |

|---------------------------------|-------------------|

| (Dr. Surapong Uttama)           |                   |

|                                 | ADVISOR           |

| (Dr. Teeravisit Laohapansaeng)  |                   |

| a selection                     | COMMITTEE         |

| (Dr. Phakphoom Boonyanant)      |                   |

| ##.                             | COMMITTEE         |

| (Dr. Sirichai Hemrungrote)      |                   |

| Joonsuk Chipipop                | EXTERNAL EXAMINER |

| (Assoc. Prof. Boonruk Chipipop) |                   |

#### **ACKNOWLEDGEMENTS**

This thesis would not have been possibly made without thanks for all help and support. First of all, I would like to express my sincere gratitude to my advisor Dr. Teeravisit Laohapensaeng and Asst. Prof. Roungsan Chaisricharoen for their continuous support for my master degree study and research. Besides, the advice given by Paweena Suebsombut has been a great help in calculating equations. Finally, the success of this thesis would not have been possible withoutthe support from my family, and I wish to express my appreciation of creating the excellent environment for education and research.

Sittan Udomsom

Thesis Title Active BALUN Based on OTA Device

**Author** Sittan Udomsom

**Degree** Master of Engineering (Computer Engineering)

**Advisor** Dr. Teeravisit Laohapensaeng

#### **ABSTRACT**

In modern communication systems, the signal splitter and combiner called BALUN (BALance to UNbalance) is required to interface a single ended device with a differential device. Most active BALUNs deploy passive elements which cannot be tuned and require large area in the integrated circuit. Though, there is the controllable BALUN based on BiCMOS CCCII, the implementing circuit is quite large in a transistor count and the cost of BiCMOS is very expensive. In this work, the new active BALUN based on CMOS OTA is proposed. By adjusting the transconductance of the composed OTAs, the characteristics of the BALUN can be tuned electronically. Normally, the size of the OTA is half of the size of the CCCII in the transistor count. Therefore, the size of the proposed structure is theoretically half of the CCCII counterpart. The design structure is simulated in the HSPICE based on the 90nm IBM RF-CMOS process parameters extracted by MOSIS. The result shows that the proposed structure can be a fair alternative in the BALUN design via adequate compatibility of the BALUN characteristics such as power-splitting, power-combination and phase inverting.

Keywords: Operational Transconductance Amplifier/ActiveBALUN/CMOS

## TABLE OF CONTENTS

|                                           | Page |

|-------------------------------------------|------|

| ACKNOWLEDGEMENTS                          | (3)  |

|                                           |      |

| ABSTRACT                                  | (4)  |

| LIST OF TABLES                            | (7)  |

| LIST OF FIGURES                           | (8)  |

| CHAPTER                                   |      |

| 1 INTRODUCTION                            | 1    |

| 1.1 Background and Problem Definition     | 1    |

| 1.2 Objective                             | 2    |

| 1.3 Scope                                 | 2    |

| 1.4 Procedure                             | 2    |

| 2 BACKGROUND THEORY AND LITERATURE REVIEW | 3    |

| 2.1 Review of BALUN                       | 3    |

| 2.2 Literature Review                     | 6    |

| 3 PROPOSED METHOD                         | 14   |

| 3.1 Power Split BALUN                     | 14   |

| 3.2 Power Combined BALUN                  | 19   |

| 4 SIMULATION RESULTS                      | 24   |

| 4.1 Simulation Tool and Method            | 24   |

| 4.2 CMOS Model                            | 25   |

| 4.3 Tranconductance Versus Current Bias   | 27   |

# **TABLE OF CONTENTS (Continued)**

|                                                          | Page |

|----------------------------------------------------------|------|

| CHAPTER                                                  |      |

| 4.4 Power Split BALUN Results                            | 29   |

| 4.5 Power Combined BALUN Results                         | 38   |

| 5 CONCLUSION                                             | 48   |

| 5.1 Results of the Simulation                            | 48   |

| 5.2 Limitations                                          | 49   |

| 5.3 Future Work                                          | 50   |

| REFERENCES                                               | 51   |

| APPENDICES                                               | 55   |

| APENDIX A Austria Microsystem SiGe BiCMOS 0.35 μm        | 56   |

| APENDIX B Tunable Active CMOS BALUN based on Operational |      |

| Transconductance Amplifier                               | 59   |

| APENDIX C Active Tunable Nanoscale CMOS BALUN Based on   |      |

| Operational Transconductance Amplifier                   | 63   |

| CURRICULUM VITAE                                         | 67   |

# LIST OF TABLES

| Tak | ole and the second seco | Page |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1 | An Overview of AMS S35D4M5 SiGe Bi-CMOS Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25   |

| 4.2 | The 90nm of an IBM 9RF CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27   |

| 4.3 | Compared Current Bias vs gm and Vdd, Vss between 0.35 Si-Ge Bi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|     | CMOS and 90 nm IBM 9RF COMS process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45   |

| 4.4 | Compared BALUN Performance between 0.35µm SiGe BiCMOS and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|     | 90 nm IBM 9RF CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46   |

## LIST OF FIGURES

| Figure                                                                    | Page |

|---------------------------------------------------------------------------|------|

|                                                                           |      |

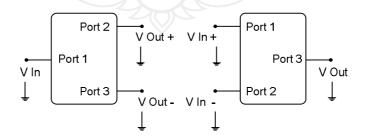

| 2.1 Basic Structure of BALUN                                              | 3    |

| 2.2 Power-split and Power Combined BALUN                                  | 3    |

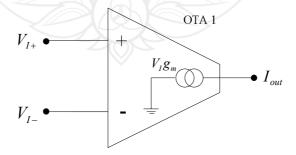

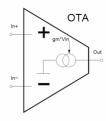

| 2.3 Schematic Symbol for the OTA                                          | 4    |

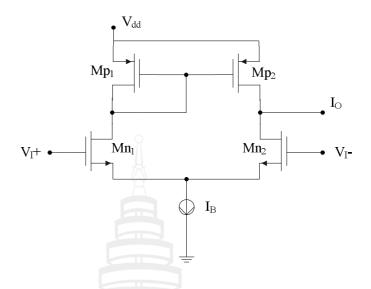

| 2.4 Transistor Level of Operational Transconductance Amplifier            | 5    |

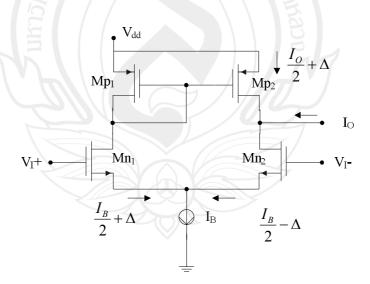

| 2.5 Transistor Level of OTA with Current Flow Path                        | 5    |

| 2.6 An Equivalent Circuit Model of Operational Transconductance Amplifier | 6    |

| 2.7 Electrical Symbolic of Transformer BALUN                              | 7    |

| 2.8 R3838 SMT Mini Wideband Transformers 3.8mm x 5.0mm                    | 7    |

| 2.9 Transformer BALUN Balun Toroid                                        | 8    |

| 2.10 Basic Schematic of Waveguide BALUN                                   | 8    |

| 2.11 Microstrip Waveguide BALUN                                           | 9    |

| 2.12 Microstrip Waveguide BALUN Built in with Dipole Antenna 2.10 and     |      |

| 2.11 Printed Dipole Antenna with Integrated Balun                         | 9    |

| 2.13 LRC Networks BALUN Narrowband BalunCalculator                        | 10   |

| 2.14 Single Transistor BALUN                                              | 11   |

| 2.15 Differential Pair Transistor BALUN                                   | 11   |

| 2.16 Blocked Level of the CCCII-based BALUN                               | 12   |

| 3.1 A Schematic of Active BALUN Using OTA                                 | 14   |

| 3.2 An Equivalent Schematic of Active BALUN                               | 16   |

| 3.3 An Equivalent Schematic of Active BALUN (Connected Voltage Source     |      |

| to Calculate z Input Impedance)                                           | 16   |

| 3.4 An Equivalent Schematic of Active BALUN (Reduced)                     | 17   |

# **LIST OF FIGURES (Continued)**

| Figure                                                                                         | Page |

|------------------------------------------------------------------------------------------------|------|

| 3.5 An Equivalent Schematic of Active BALUN (Connected Voltage Source                          |      |

| to Calculate z Output Impedance)                                                               | 18   |

| 3.6 An Equivalent Schematic of Active BALUN (Reduced)                                          | 18   |

| 3.7 A Schematic of Power Combined Active BALUN Using OTA                                       | 19   |

| 3.8 An Equivalent Model of Power Combined Active BALUN                                         | 20   |

| 3.9 An Equivalent Schematic Used to Calculate Impedance of an Input of                         |      |

| Power Combined Active BALUN                                                                    | 21   |

| 3.10 An Equivalent Schematic Used to Calculate Impedance of an Input of                        |      |

| Power Combined Active BALUN (Reduced)                                                          | 21   |

| 3.11 An Equivalent Schematic Used to Calculate Impedance of an Output of                       |      |

| Power Combined Active BALUN                                                                    | 22   |

| 3.12 An Equivalent Schematic Used to Calculate Impedance of an Output of                       |      |

| Power Combined Active BALUN (Reduced)                                                          | 22   |

| 4.1 HSPICE                                                                                     | 25   |

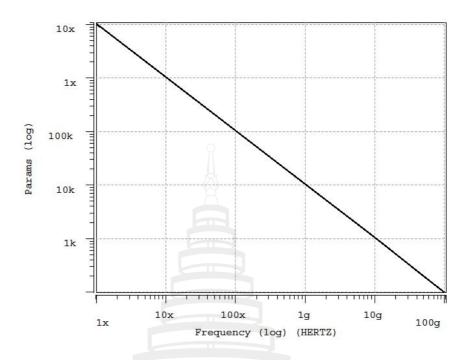

| 4.2 A Transconductance (g <sub>m</sub> ) Related to I <sub>B</sub> bias of 0.35 μm Si-GeBiCMOS | 28   |

| 4.3 A Transconductance (g <sub>m</sub> ) Related to I <sub>B</sub> BiasBased on IBM 9RF 90nm   |      |

| CMOS                                                                                           | 28   |

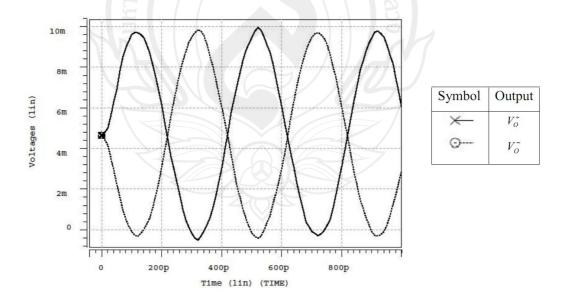

| 4.4 Result of 100 μA Current Bias for OTA 3 and OTA 4 with Output from                         |      |

| $V_o^+$ and $V_o^-$                                                                            | 29   |

| 4.5 Result of 100 μA Current Bias for OTA 3 and OTA 4 with Voltage Output                      |      |

| from Differential Output Compared to Input                                                     | 30   |

# **LIST OF FIGURES (Continued)**

| Figu | ire                                                                     | Page |

|------|-------------------------------------------------------------------------|------|

| 4.6  | Result of 200 μA Current Bias for OTA 3 and OTA 4 with Output           |      |

|      | from $V_o^+$ and $V_o^-$                                                | 30   |

| 4.7  | Result of 200 $\mu A$ Current Bias for OTA 3 and OTA 4 with Output      |      |

|      | Voltage from Differential Output Compared to Input.                     | 31   |

| 4.8  | Result of 300 $\mu A$ Current Bias for OTA 3 and OTA 4 with Output from |      |

|      | $V_o^+$ and $V_o^-$                                                     | 31   |

| 4.9  | Result of 300 $\mu A$ Current Bias for OTA 3 and OTA 4 with Output      |      |

|      | Voltage from Differential Output Compared to Input                      | 32   |

| 4.10 | Result of 300 µA Current Bias for OTA 3 and OTA 4 with Voltage          |      |

|      | Differential Output in 1 GHz Frequencies Range in dB                    | 32   |

| 4.11 | Result of 300 $\mu A$ Current Bias for OTA 3 and OTA 4 with Phase       |      |

|      | Imbalance of Differential Output                                        | 33   |

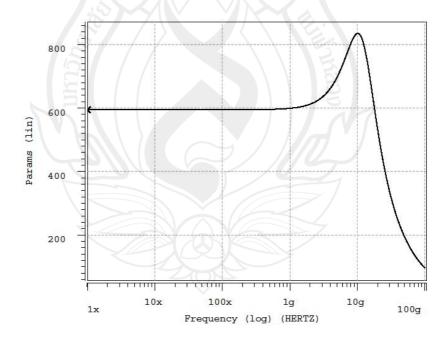

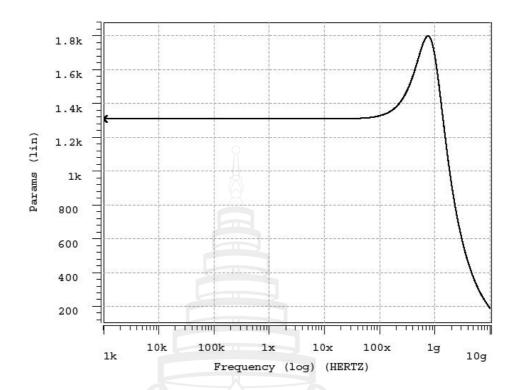

| 4.12 | Frequencies Response of Input Impedance Power Split BALUN               |      |

|      | in Ohm Versus Frequencies                                               | 33   |

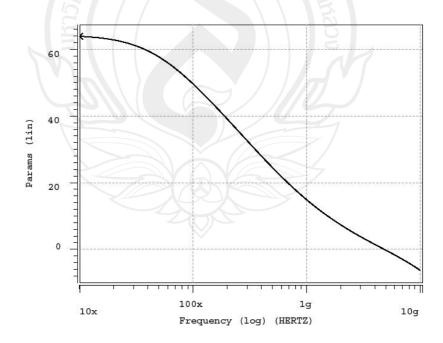

| 4.13 | Frequencies Response of Positive Output Impedance Power Split           |      |

|      | BALUN in Ohm Versus Frequencies                                         | 34   |

| 4.14 | Frequencies Response of Negative Output Impedance Power Split           |      |

|      | BALUN in Ohm Versus Frequencies                                         | 34   |

| 4.15 | Frequencies Response and dB from $V_o$ Output of Power Split BALUN,     |      |

|      | -3dB Bandwidth is15.7GHz                                                | 35   |

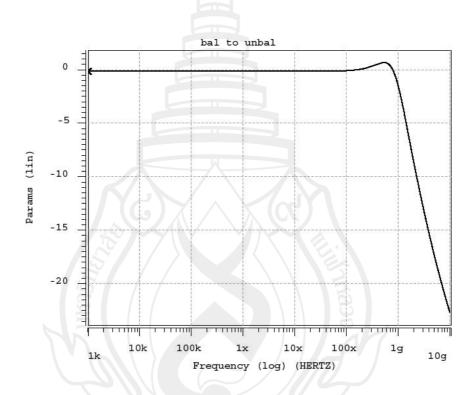

| 4.16 | Frequencies Response of Phase Differential 180 Degree Output from       |      |

|      | Power Split BALUN with 7.14° of Phase Imbalance at -3dB                 |      |

|      | (15.7GHz).                                                              | 36   |

# LIST OF FIGURES (continued)

| Figu | re                                                                    | Page |

|------|-----------------------------------------------------------------------|------|

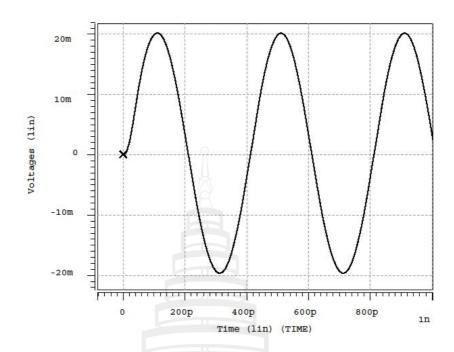

| 4.17 | Differential Output of Power Split BALUN Transient Analysis for Input |      |

|      | 10mV at 2.5GHz                                                        | 36   |

| 4.18 | Frequencies Response of Input Impedance from Power Split              |      |

|      | BALUN                                                                 | 37   |

| 4.19 | Frequencies Response of Positive Output Impedance from Power          |      |

|      | Split BALUN                                                           | 37   |

| 4.20 | Frequencies Response of Negative Output Impedance                     |      |

|      | from Power Split BALUN                                                | 38   |

| 4.21 | Frequencies Response and dB from $V_o$ Output of Power                |      |

|      | Combined BALUN, -3dB Bandwidth is1.19 GHz                             | 39   |

| 4.22 | A Transient Analysis of Combined Output of Power Combined             |      |

|      | BALUN for 2 Input of 50mV PP which 180° Out Phase at 10               | 39   |

|      | MHz                                                                   |      |

| 4.23 | Frequencies Response of Positive Input Impedance from                 |      |

|      | Power Combined BALUN                                                  | 40   |

| 4.24 | Frequencies Response of Negative Input Impedance from                 |      |

|      | Power Combined BALUN                                                  | 40   |

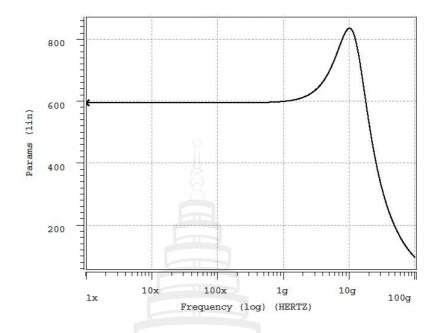

| 4.25 | Frequencies Response of Output Impedance from Power                   |      |

|      | Combined BALUN                                                        | 41   |

| 4.26 | CMRR Frequencies Response of Power Combined BALUN                     | 41   |

# LIST OF FIGURES (continued)

| Figu | re                                                              | Page |

|------|-----------------------------------------------------------------|------|

| 4.27 | Frequencies Response and dB from $V_o$ Output of Power Combined |      |

|      | BALUN, -3dB Bandwidth is17.5 GHz                                | 42   |

| 4.28 | A Transient Analysis of Combined Output of Power Combined       |      |

|      | BALUN for 2 Inputs of 10mV PP which 180° Out Phase at           |      |

|      | 2.5GHz.                                                         | 43   |

| 4.29 | Frequencies Response of Z Impedance from Power                  |      |

|      | Combined BALUN Positive Input                                   | 43   |

| 4.30 | Frequencies Response of Z Impedance from Power                  |      |

|      | Combined BALUN Negative Input                                   | 44   |

| 4.31 | Frequencies Response of Z Impedance from Power                  |      |

|      | Combined BALUN Output                                           | 44   |

| 4.32 | Frequencies Response of Power Combined BALUN                    |      |

|      | CMRR                                                            | 45   |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background and Problem Definition

Nowadays, most transceivers are composed of both single ended (SE) and differential ended (DE) components. Therefore, a converter circuit called the BALanced to UNbalanced (BALUN) converter is usually needed. Most BALUN designs are based on passive components, BJT, and BiCMOS. Though these designs work well on their own, most transceivers are favored to be fabricated based only on complementary MOS (CMOS) to be placed among various digital functions. In addition, ability in tuning is also a good option in the BALUN to cover errors in gain matching that are likely to occur with quite high probability in practical systems. Interestingly, the operational transconductance amplifier (OTA) simulating voltagecontrolled current source (VCCS) is one of the favorite active analogue devices because the transconductance can be tuned electronically via bias current. Therefore, key properties of its applications can be easily tuned via single or multiple bias current. In addition, the OTA is usually small compared to the current controlled current conveyor (CCCII) which formerly composes a tunable active BALUN. In this paper, the novel active nanoscale CMOS BALUN is proposed based on the OTAs. The proposed circuit will be easily placed in a mixed signal chip because it requires no passive elements and no different types of transistors.

#### 1.2 Objective

To design and simulate a new active BALUN based on an OTA device using AMS 0.35u Si-GeBiCMOS and IBM 90nm 9RF CMOS MOSFET model.

#### 1.3 Scope

- 1.3.1 The new active BALUN will be based on CMOS OTA.

- 1.3.2 The simulated MOSFET model is based on the AMS  $0.35\mu$  Si-GeBiCMOS and IBM 90nm 9RF CMOS.

- 1.3.3 Performance simulations will be conducted by the HSPICE.

#### 1.4 Procedure

- 1.4.1 Study structures and characteristics of BALUN.

- 1.4.2 Study structures and characteristics of OTA.

- 1.4.3 Design an OTA active BALUN.

- 1.4.4 Simulate performance by the HSPICE.

- 1.4.5 Analyze results.

- 1.4.6 Adjust the design to fit the required performance.

#### **CHAPTER 2**

#### **BACKGROUND THEORY AND LITERATURE REVIEW**

#### 2.1 Review of BALUN

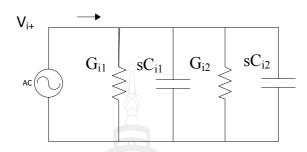

A BALUN is a device for conversion between a single-ended signal and a differential signal. The differential signal can be considered as two signals with equal voltage but 180° antiphase. A high performance BALUN design is critical for integrating the single-ended and differential signals. Bandwidth, phase and magnitude imbalances are all the important issues in the BALUN design (Figure 2.1).

Figure 2.1 Basic Structure of BALUN

Figure 2.2 Power Split and Power Combined BALUN

#### 2.1.1 Characteristic Parameters of BALUN

Consider the BALUN as a power splitter and combiner (Figure 2.2). Ideally, the signals at the two differential ports are equal in magnitude and 180° out of phase for all frequencies, but in practice, the magnitudes of differential output voltageare slightly different (amplitude imbalance), there exists a phase imbalancebetween the two output signals away from the ideal 180° difference. Generally, BALUNs are required to show 50-characteristic impedances at all the ports.

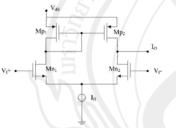

#### **2.1.2** What is OTA?

The operational transconductance amplifier (OTA) is an amplifier whose differential input voltage produces an output current. Thus, it is a voltage controlled current source (VCCS) (Gnecchi, 2010). There is usually an additional input for a current to control the amplifier's transconductance. The OTA is similar to a standard operational amplifier in that it has a high impedance differential input stage and that it may be used with negative feedback.

The ideal transfer characteristic is

$$I_{\text{out}} = g_m (V_{In+} - V_{in-})$$

(1)

Or, by taking the pre-computed difference as the input,

$$I_{\text{out}} = g_m V_{ln} \tag{2}$$

Figure 2.3 Schematic Symbols for the OTA.

Figure 2.4 Transistor Level of Operational Transconductance Amplifier

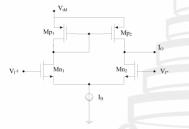

For a new solution of BALUN, considering a schematic diagram of OTA device, the transistor level of the OTA is used in a positive part as shown in Figure  $3.1.\ V_{I}$ + and  $V_{I}$ - are applied to  $Mn_1$  and  $Mn_2$  as inputs of acircuit.

Figure 2.5 Transistor Level of OTA with Current Flow Path

From the current flow path in Figure 3.1, the current entering I<sub>O</sub> is

$$I_O = \frac{I_B}{2} - \Delta - \frac{I_B}{2} - \Delta \tag{3}$$

Therefore

$$I_{o} = -2\Delta$$

(4)

For an equivalent circuit model of an OTA

Figure 2.6 An Equivalent Circuit Model of Operational Transconductance Amplifier

#### 2.2 Literature Review

#### 2.2.1 Passive Element BALUN

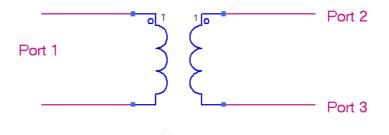

The simple BALUN transformer was made by twisting a pair of magnets wired around ferrites. To make a single-ended signal on a primary side, a negative port was connected to ground and two secondary ports were connected to differential inputs. With a characteristic of the transformer, BALUN could give an impedance transformation. A major problem of this type of BALUN was a larger size of incapacity.

Figure 2.7 Electrical Symbolic of Transformer BALUN

**From** MPS Industries. (n.d.). **Balun transformers.** Retieved August 18, 2012, from http://www.mpsind.com/MPS-pages/MPS-product-pages/baluntransformers.html

Figure 2.8 R3838 SMT Mini Wideband Transformers 3.8mm x 5.0mm

From Wendell, R. J. (n.d.). WBØJNR: My amateur radio station. Retieved August 18, 2012, from http://www.rogerwendell.com/mystation.html

Figure 2.9 Transformer BALUN Balun Toroid

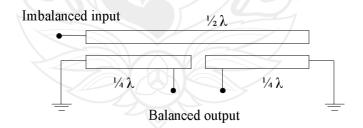

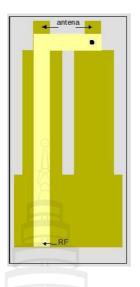

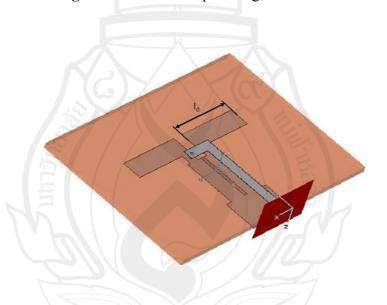

The second BALUN method was to use planar waveguides or microstrip transmission lines or coaxial cable BALUN. This type of BALUN provided bandwidth capability by using quarter-wave lines as long as the center frequencies, but requiring a large area for wavelengths.

Figure 2.10 Basic Schematic of Waveguide BALUN

Figure 2.11 Microstrip Waveguide BALUN

From Chuang, H. R. & Kuo, L. C. (2003). 3-D FDTD Design Analysis of a 2.4-GHz Polarization-Diversity Printed Dipole Antenna with Integrated Balun and Polarization-Switching Circuit for WLAN and Wireless Communication Applications. IEEE Transactions on Microwave Theory and Techniques, 51(2), 374-381.

**Figure 2.12** Microstrip Waveguide BALUN Built in with Dipole Antenna 2.10 and 2.11 Printed Dipole Antenna with Integrated Balun

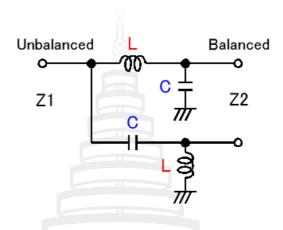

The third one was called LRC Networks BALUN. There were benefits for small form factors and a high potential for integration, however, it could only be tuned in to a narrow band and sometimes unattainable to reduce imbalances due to being a passive device

Figure 2.13 LRC Networks BALUN Narrowband BalunCalculator

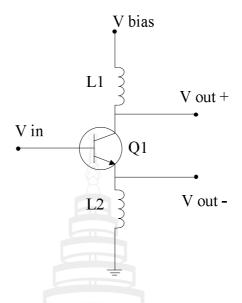

#### 2.2.2 Transistor Based BALUN

The simplest active implementation of BALUN is to use a single transistor (Figure 2.14). The inputs fed to the base and the differential signals are tapped at the collector and emitter. The input signals are applied to the base (Input) and the outputs are taken from both the emitter (+) and the collector (-) (Roozbahani, 2004). The phase output signals are correspondingly 180° from each other, and thus produce a balanced signal from an unbalanced one.

Figure 2.14 Single Transistor BALUN

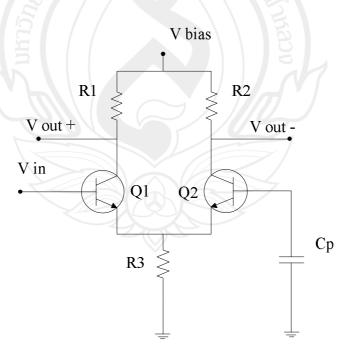

The classic common-emitter differential pair (Baker, 2010). Can be converted to a BALUN by grounding one of the inputs through a capacitor.

Figure 2.15 Differential Pair Transistor BALUN

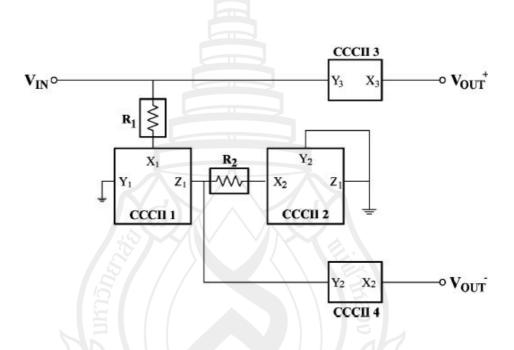

#### 2.2.3 CCCII BALUN

The second-generation current-controlled conveyor (CCCII) is a popular building block for analog electronics functions at baseband, RF, and video frequencies. The CCCII is composed of three input-output ports using BALUN (Godara & Fabre, 2007), and 4 blocks of the CCCII are in operation. The problem is the CCCII structure needs a large number of transistors and MOSs so this structure needs more area for chips, is expensive, and has more CMOS error problems from industrial lines.

From Godara, B. & Fabre, A. (2008). A highly compact active wideband balun with impedance transformation in SiGeBiCMOS. **IEEE Transactions on Microwave Theory and Techniques**, **56**(1), 22-30.

Figure 2.16 Blocked Level of the CCCII-based BALUN

As previously mentioned, the passive BALUN needs a large space which varies inversely with frequency and is difficult to be adjusted to fit the required frequency, for example, transformer BALUN, wavelength BALUN and RLC BALUN. The problem can be solved by using an active BALUN circuit with a single

transistor or differential pair transistor which helps decrease the size of the circuit and is easier to be adjusted to fit the required frequency.

However, there are still some limitations to how each type of transistors works based on its characteristics and quality (Cooke, 1971), including passive sessions in the circuit because it cannot be used in high-frequency range or wide bandwidth. For less space of use, an active BALUN using a CCCII module is introduced asit needs much smaller space because it is fabricated on Bi-CMOS. The characteristics of the CCCII can make the BALUN used in wider frequency and the impedance adjusted to fit the required frequency.

Nevertheless, the structure of the CCCII is complicated because there are various types of transistors. This causes the fabricated procedure on the Bi-CMOS (Larson, 1998) to be more expensive and larger size than the active OTA BALUN presented in this research.

#### **CHAPTER 3**

#### PROPOSED METHOD

#### 3.1 Power Split BALUN

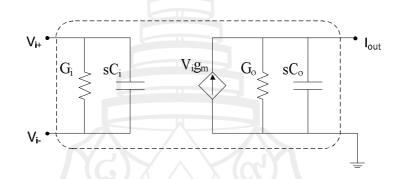

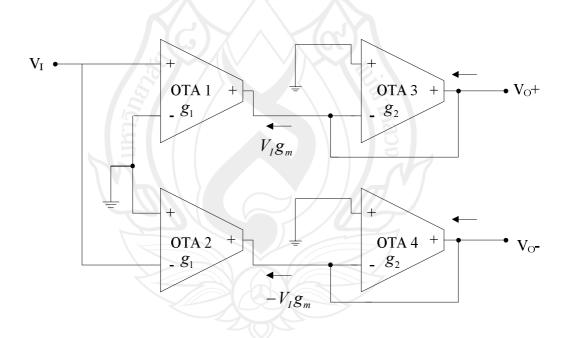

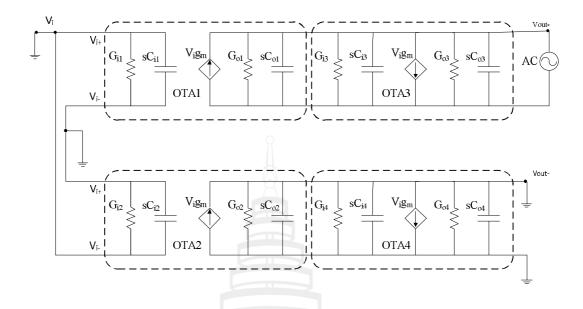

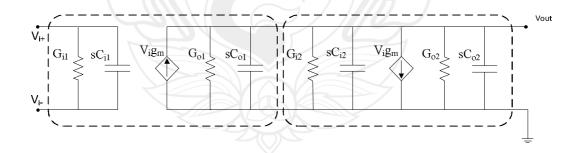

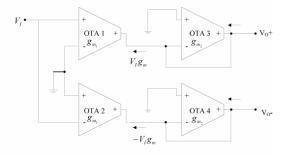

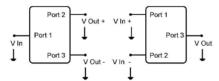

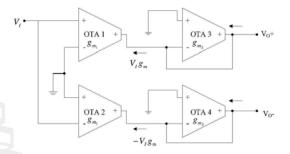

To build a complete OTA active BALUN shown in Figure 3.1, OTA 1 and OTA 2 are used as power-splitter and anti-phase. OTA 3 and OTA 4 work as pre-load function to adjust the outputs.

Figure 3.1 A Schematic of Active BALUN Using OTA

From Figure 3.1, the equation for  $V_o^+$  is shown as follows:

$$V_I g_1 - V_O^+ g_2 = 0 (5)$$

Therefore

$$V_O^+ = V_I \frac{g_1}{g_2} \tag{6}$$

For  $V_O^-$

$$\left(-V_{I}g_{1}\right)+\left(-V_{O}^{-}g_{2}\right)=0\tag{7}$$

Therefore

$$V_O^- = -V_I \frac{g_1}{g_2} \tag{8}$$

From (10) and (12),  $V_{\rm O}$  should be

$$V_o = V_I \left(\frac{2g_1}{g_2}\right) \tag{9}$$

Then

$$g_2 = 2g_1 \tag{10}$$

And

$$V_O \cong V_I \tag{11}$$

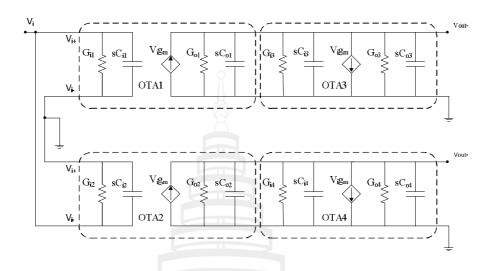

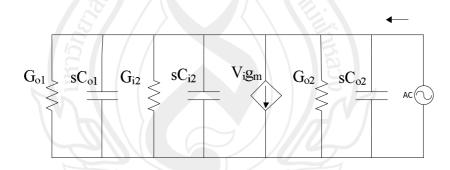

An equivalent circuit of power split BALUN is shown in Figure 3.2.

Figure 3.2 An Equivalent Schematic of Active BALUN

To calculate input impedance of power split BALUN connected voltage source to an input port and connect an output port to ground, then measure and calculate a voltage source current output or  $I_{\rm i}$

**Figure 3.3** An Equivalent Schematic of Active BALUN (Connected Voltage Source to Calculate z Input Impedance)

#### Reduced to

Figure 3.4 An Equivalent Schematic of Active BALUN (Reduced)

Assume that

$$G_{i_1} = G_{i_2} \tag{12}$$

And

$$sC_{i_1} = sC_{i_2}$$

(13)

So

$$I_i = V_i 2(G_i + sC_i) \tag{14}$$

Then

$$Z_{in} = \frac{V_i}{I_i} = \frac{1}{2G_i + s2C_i}$$

(15)

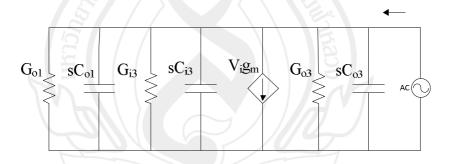

To calculate output impedance of each part by connecting positive outputs to a voltage current source, then negative outputs and inputs to ground.

**Figure 3.5** An Equivalent Schematic of Active BALUN (Connected Voltage Source to Calculate z Output Impedance)

Reduced to

Figure 3.6 An Equivalent Schematic of Active BALUN (Reduced)

Then I is equal to

$$I_{i} = V_{i} \left( g_{m_{2}} + G_{i_{3}} + G_{0_{1}} + G_{0_{3}} + s \left( C_{i_{3}} + C_{o_{1}} + C_{o_{3}} \right) \right)$$

(16)

So the output impedance should be

$$Z_{out} = \frac{1}{\left(g_{m_2} + G_{i_3} + G_{0_1} + G_{0_3} + s\left(C_i + C_{o_1} + C_{o_{32}}\right)\right)}$$

(17)

Or assume that  $G_{i_3} + G_{o_1} + G_{o_3}$  are near to zero when compared  $g_{m_2}$  to

$$Z_{out} \cong \frac{1}{\left(g_{m_2} + s\left(C_{i_3} + C_{o_1} + C_{o_3}\right)\right)}$$

(18)

then the output voltage in each side can be calculated in the equivalent cuicuit

$$V_{o^{\pm}} = \frac{V_{I}(g_{m} + G_{I_{1}} + G_{I_{2}} + s(C_{I_{1}}))}{g_{m_{2}} + G_{O_{1}} + G_{O_{2}} + s(C_{I_{2}} + C_{O_{1}} + C_{O_{2}})}$$

(19)

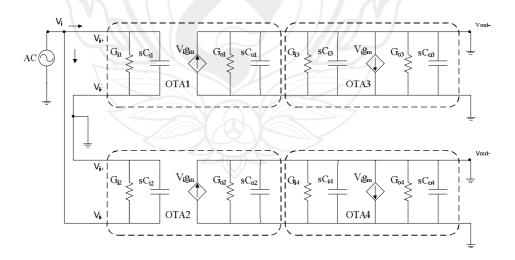

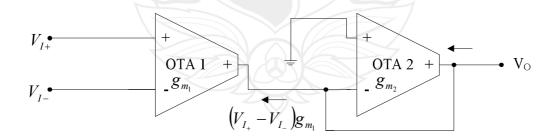

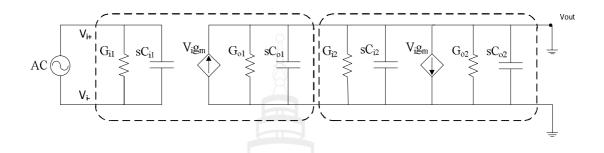

#### 3.2 Power Combined BALUN

The structure for a signal combining BALUN is shown in Figure. 3.7. The OTA 1 is used as an input stage and the OTA 2 acts as a pre-load device.

Figure 3.7 A Schematic of Power Combined Active BALUN Using OTA

The nodal analysis is taken at the output of OTA 1 which gives:

$$(V_{I_{+}} - V_{I_{-}})g_{m_{1}} - V_{O}g_{m_{2}} = 0$$

(20)

Therefore

$$V_{O} = \left(V_{I_{+}} - V_{I_{-}}\right) \frac{g_{m_{1}}}{g_{m_{2}}} \tag{21}$$

To make the input and output power equal, the following criteria must be met.

$$g_{m_2} = g_{m_1} \tag{22}$$

Therefore, a single ended output power is the same as the differential input power

$$V_O \cong \left(V_{I_+} - V_{I_-}\right) \tag{23}$$

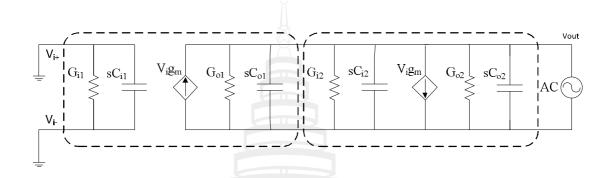

Or by taking an equivalent model

Figure 3.8 An Equivalent Model of Power Combined Active BALUN

To calculate input impedance by an equivalent model to connect a voltage source to input and connect an output to ground.

**Figure 3.9** An Equivalent Schematic Used to Calculate Impedance of an Input of Power Combined Active BALUN

Reduced to  $\begin{array}{c|c} V_i & & \\ \hline & G_{i1} & \\ \hline & & \\ \end{array}$

Figure 3.10 An Equivalent Schematic Used to Calculate Impedance of an Input of Power Combined Active BALUN (Reduced)

To calculate  $I_i$  assume that

$$I_i = V_i \left( G_i + sC_i \right) \tag{24}$$

Then input impedance is equal to

$$Z_{in} = \frac{V_i}{I_i} = \frac{1}{G_i + sC_i}$$

(25)

**Figure 3.11** An Equivalent Schematic Used to Calculate Impedance of an Output of Power Combined Active BALUN

Figure 3.12 An Equivalent Schematic Used to Calculate Impedance of an Output of Power Combined Active BALUN (Reduced)

Then I is equal to

$$I_{i} = V_{i} \left( g_{m_{2}} + G_{i_{2}} + G_{0_{1}} + G_{0_{2}} + s \left( C_{i_{2}} + C_{o_{1}} + C_{o_{2}} \right) \right)$$

(26)

So output impedance should be

$$Z_{out} = \frac{1}{\left(g_{m_2} + G_{i_2} + G_{0_1} + G_{0_2} + s\left(C_{i_2} + C_{o_1} + C_{o_2}\right)\right)}$$

(27)

Or assume that  $G_{i_3} + G_{o_1} + G_{o_3}$  are near to zero when compared  $g_{m_2}$  to

$$Z_{out} \cong \frac{1}{\left(g_{m_2} + s\left(C_{i_2} + C_{o_1} + C_{o_2}\right)\right)}$$

(28)

Then the output voltage in each side can be calculated in the equivalent cuicuit

$$V_{o} = \frac{\left(V_{I^{+}} - V_{I^{-}}\right)\left(g_{m} + G_{I_{1}} + G_{I_{2}} + s\left(C_{I_{1}}\right)\right)}{g_{m_{2}} + G_{O_{1}} + G_{O_{2}} + s\left(C_{I_{2}} + C_{O_{1}} + C_{O_{2}}\right)}$$

(29)

## **CHAPTER 4**

## SIMULATION RESULTS

### 4.1 Simulation Tool and Method

To verify the validity of the proposed BALUN, the transient, frequency response of signal splitters, transconductance and Z impedance was simulated by HSPICE 2007.3 with two environments 0.35  $\mu m$  SiGe BiCMOS model and 90 nm IBM 9RF-CMOS process.

## 4.1.1 Experimental Environment

Simulator

HSPICE® is the industry's most popular simulator for accurate circuit simulation and offers foundrycertified MOS device models with state-of-the-art simulation and analysis algorithms. Analog/RF/mixed-signal IC design, cell and memory characterization, and chip/package/board/backplane signal integrity simulation are also widely used. In this research, HSPICE® on version 2003.7 is used. SPICE stands for Simulation Program with Integrated Circuit Emphasis. It is the predominant tool used to simulate circuits, and was developed at UC Berkeley in the 1970s. "H" in HSPICE means to be commercialized by Shawn and Kim Hailey of Meta Software. To analyze a circuit and plot the results of an analysis with a tool called Avanwaves.

Figure 4.1 HSPICE

## 4.2 CMOS Model

## 4.2.1 AMS 0.35 µm SiGe BiCMOS

For this simulation,  $0.35~\mu m$  SiGe BiCMOS design kit provided by the Austria Microsystems was used and this fabricated model was used for HSPICE simulator. The  $0.35\mu m$  SiGe BiCMOS process is based on  $0.35\mu m$  mixed-signal CMOS process (Kelly, Power, Oapos & Neill, 2003) with low noise MOS transistors .In this thesis, an AMS S35D4M5SiGe Bi-CMOS was used as a fabricated model, and another option of CMOS I/O transistors voltage is 3.3/5V.

Table 4.1 An Overview of AMS S35D4M5 SiGe Bi-CMOS Technology

| <b>Process Technology Specifications</b> | Units | S35D4M5    |

|------------------------------------------|-------|------------|

| Drawn MOS Channel Length                 | μm    | 0.35       |

| Drawn Emitter Width                      | μm    | 0.4        |

| Operating Voltage CMOS                   | V     | 3.3 and 5V |

| Number of Metal Layers                   | #     | 4          |

Table 4.1 (Continued)

| Process Technology Specifications | Units          | S35D4M5      |

|-----------------------------------|----------------|--------------|

| Number of Poly Layers             | #              | 4            |

| Substrate Type                    |                | p            |

| Diffusion Pitch                   | μm             | 0.9          |

| Metal1/2/3 Pitch                  | μm             | 0.95/1.1/1.2 |

| Polyl Pitch                       | μm             | 0.8          |

| Thick Metal 4 pitch               | μm             | -            |

| High Resistive Poly               | kOhm/#         | -            |

| Poly1 / Poly2 Precision Caps      | fF/μm²         | 0.9          |

| Metal 2 / Metal 3 Precision Caps  | $fF/\mu m^2$   | 1.25         |

| N/PMOS Active Channel Length      | μm             | 0.30/0.30    |

| N/PMOS Saturation Current         | μ <b>A</b> /μm | 540/240      |

| Gain                              | (CC)-          | 160          |

| Early Voltage VAF                 | V              | 100          |

| HS-HBT: BVceo                     | V              | 2.7          |

| ft / fmax                         | GHz            | 60 70        |

**From Euro Practice-IC.** (2012). Retieved August 18, 2012, from http://www.europractice-ic.com/technologies\_AMS.php?tech\_id=SiGe

### 4.2.2 IBM 90 nm RF CMOS

On IBM 90 nm CMOS process which has 9SF, 9LP and 9RF due to different applications in this research, 9RF fabricated model for HSPICE simulatoris used by MOSIS. The 90 nm CMOS containing 5-10 metal layers (Bohr, 2002). low voltage and using copper as metallization with low-k dielectric technologymakes this process ideally suitable for a wide range of high performance RF applications up to 140 GHz of ft.

**Table 4.2** The 90 nm of an IBM 9RF CMOS

| Feature             | Unit          | 9RF             |

|---------------------|---------------|-----------------|

| Process Generation  | (nm)          | 90              |

| Lpoly               | (nm)          | 63              |

| Vdd                 | (V)           | 1.0/1.2         |

| I/O Voltage Options | (V)           | 1.8/2.5/3.3 tol |

| Std SRAM cell       | $(\mu m^2)$   | 1.21            |

| Dense SRAM cell     | $(\mu m^2)$   | .99             |

| Levels of Metal     | #             | 5-10            |

| Metallization       |               | Cu              |

| Dielectric          | (ILD)         | Low-k           |

| Power               | (uW/MHz/gate) | 0.006           |

| Density             | (Kgates/mm2)  | 400             |

| MIMCap.             | (fF/um2)      | 1.0             |

| Varactor            |               | Mos             |

| Analog thick metal  |               | yes             |

From Mecke, J. (2004). IBM Foundry Offeringsoundry Offerings. Retrieved August 21, 2012, form http://www.gobookee.com/get\_book.php?u=aHR0c DovL3cyLmNhZGVuY2UuY29tL3doaXRlcGFwZXJzL3dpcmVsZXNzX3N vbHV0aW9uc19zYW5kaWVnb18wMTA2MDUucGRmCklCTSBGb3VuZH J5IE9mZmVyaW5ncyAtIENhZGVuY2UgRGVzaWduIFN5c3RlbXM=

## 4.3 Tranconductance Versus Current Bias

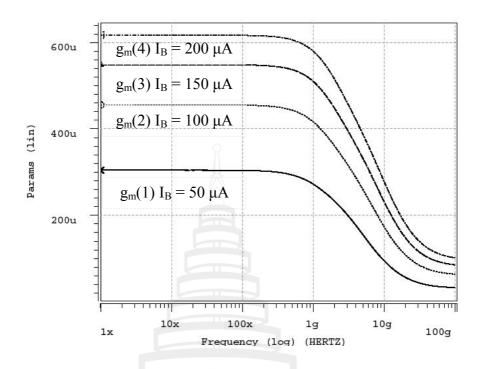

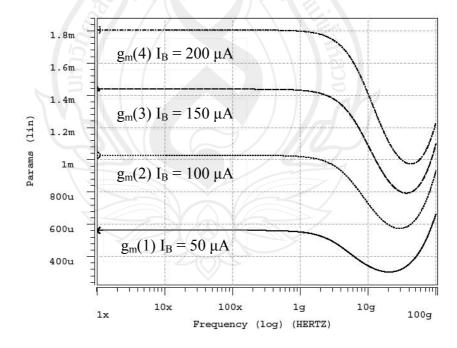

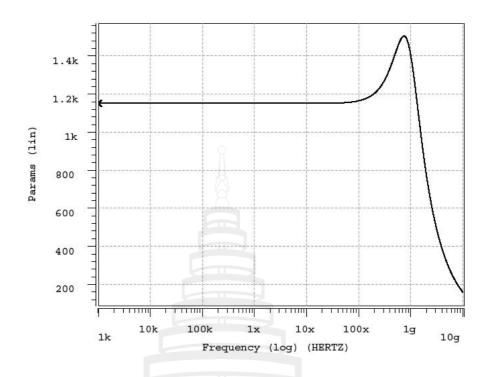

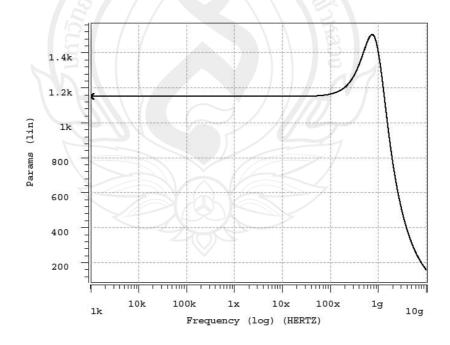

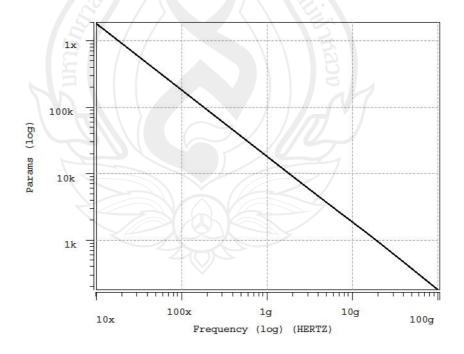

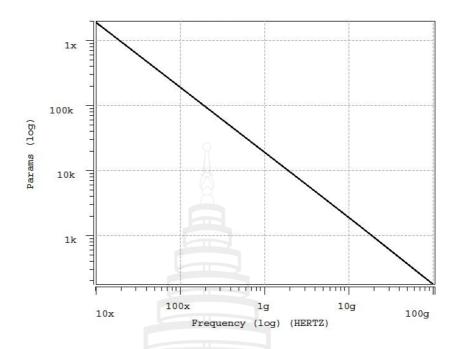

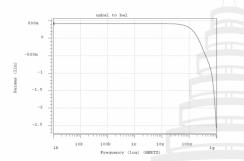

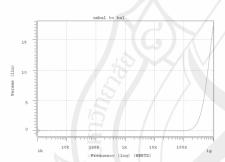

To show that transconductance ( $g_m$ ) of an OTA can be adjusted by changing current bias ( $I_B$ ). In this simulation, 0.35  $\mu m$  SiGe BiCMOS and 90 nm 9RF CMOS is biased by the same current of 50  $\mu A$ , 100  $\mu A$ , 150  $\mu A$  and 200  $\mu A$ ., and voltage input in AC analysis is 1 V. The result is shown in the figure below.

Figure 4.2 A Transconductance  $(g_m)$  Related to  $I_B$  bias of 0.35  $\mu m$  Si-GeBiCMOS

Figure 4.3 A Transconductance (g<sub>m</sub>) Related to I<sub>B</sub> bias Based on IBM 9RF 90nm CMOS

## 4.4 Power Split BALUN Results

## 4.4.1 Results from 0.35 µm SiGe Bi-CMOS Power Split BALUN

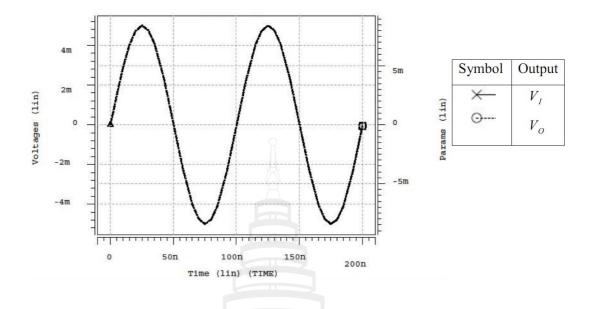

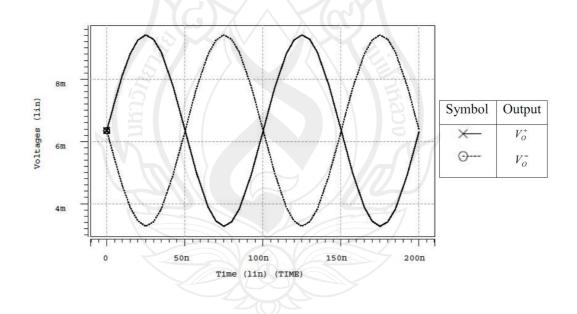

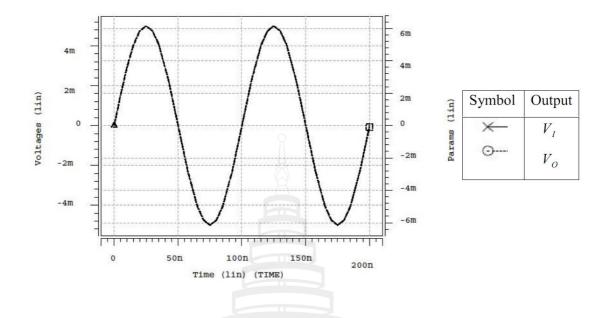

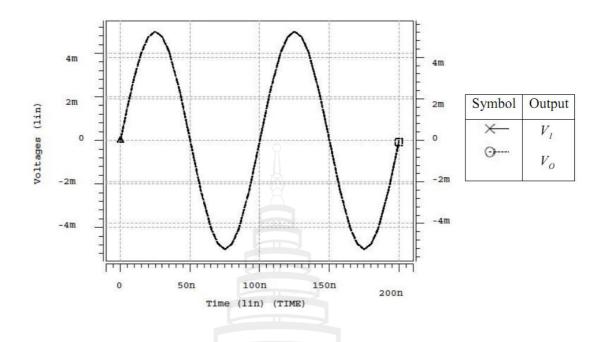

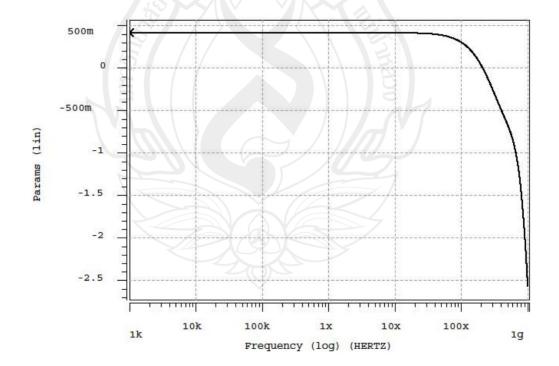

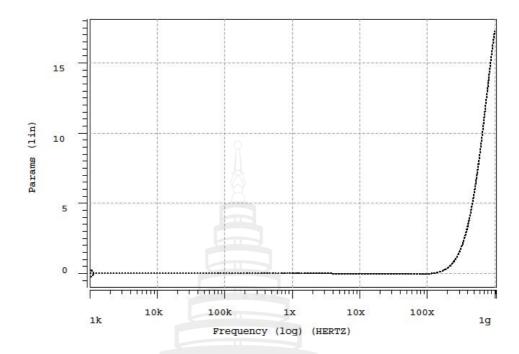

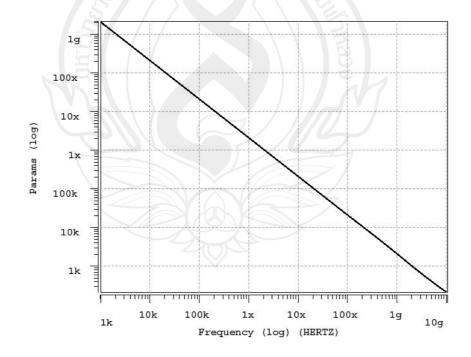

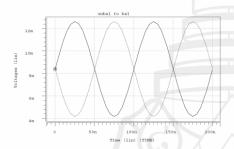

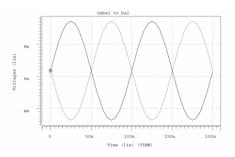

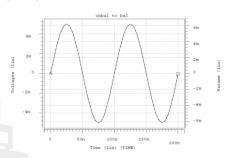

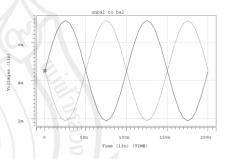

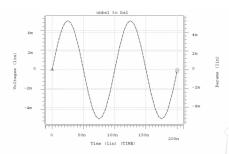

The output magnitudes are shown in Figures 4.4, 4.6 and 4.8; then Figures 4.5, 4.7 and 4.9 shows the differential signals between output and input. For AMS 0.35 Si-GeBiCMOS simulation, a small sine wave signal input of 10 mV PP at 10 MHz is used and the current bias of OTA 1 and OTA2 are 75  $\mu$ A. The tunable current of OTA 3 and OTA 4 are in steps of 100  $\mu$ A, 200  $\mu$ A and 300  $\mu$ A to show the tunable output magnitude.

The results of the different frequency ranges and phase imbalances are shown in Figure 4.4 and Figure 4.5 which the current bias of OTA 1 and OTA 2 are 75  $\mu A$  and the current bias of OTA 3 and OTA 4 are 300  $\mu A$ .

**Figure 4.4** Result of 100  $\mu$ A Current Bias for OTA 3 and OTA 4 with Output from  $V_o^+$  and  $V_o^-$

**Figure 4.5** Result of 100 μA Current Bias for OTA 3 and OTA 4 with Voltage Output from Differential Output Compared to Input

**Figure 4.6** Result of 200  $\mu$ A Current Bias for OTA 3 and OTA 4 with Output from  $V_o^+$  and  $V_o^-$

**Figure 4.7** Result of 200 μA Current Bias for OTA 3 and OTA 4 with Output Voltage from Differential Output Compared to Input

**Figure 4.8** Result of 300  $\mu$ A Current Bias for OTA 3 and OTA 4 with Output from  $V_o^+$  and  $V_o^-$

**Figure 4.9** Result of 300 μA Current Bias for OTA 3 and OTA 4 with Output Voltage from Differential Output Compared to Input

Figure 4.10 Result of 300 μA Current Bias for OTA 3 and OTA 4 with Voltage Differential Output in 1 GHz Frequencies Range in dB

**Figure 4.11** Result of 300 μA Current Bias for OTA 3 and OTA 4 with Phase Imbalance of Differential Output

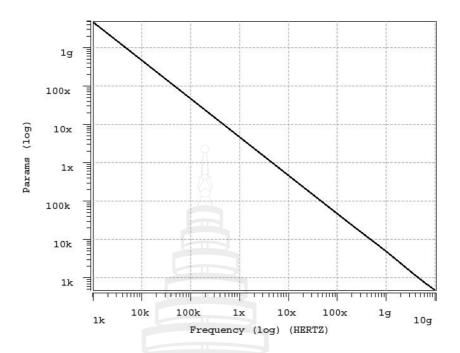

Figure 4.12 Frequencies Response of Input Impedance Power Split BALUN in Ohm Versus Frequencies

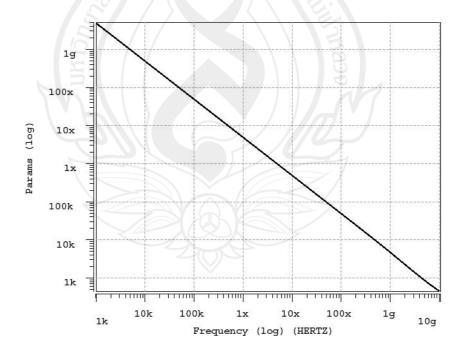

Figure 4.13 Frequencies Response of Positive Output Impedance Power Split BALUN in Ohm Versus Frequencies

**Figure 4.14** Frequencies Response of Negative Output Impedance Power Split BALUN in Ohm Versus Frequencies

## 4.4.2 Results from IBM 9RF CMOS Power Split BALUN

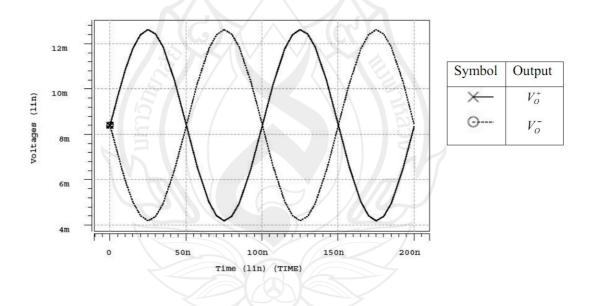

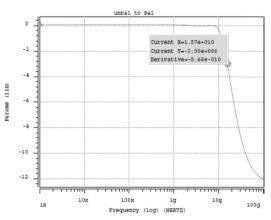

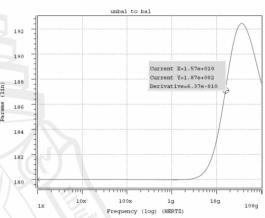

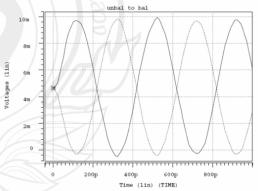

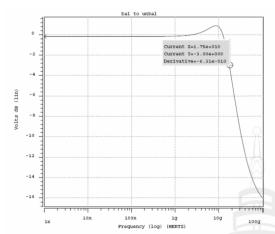

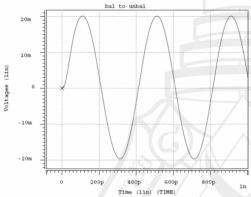

To verify the validity of the 90 nm RF CMOS BALUN based on the 90 nm IBM RF-CMOS process extracted by the MOSIS. For power split BALUN, the bias currents are 80  $\mu$ A for OTA 1 and 2, and 172  $\mu$ A for OTA 3 and 4. The frequencies responses are shown in Figure 4.15. Phase imbalance is shown in Figure 4.16. The transient response from 2.5GHz 10mV PP input is plotted in Figure 4.17, and z-impedance is shown in Figure 4.18, 4.19, and 4.20.

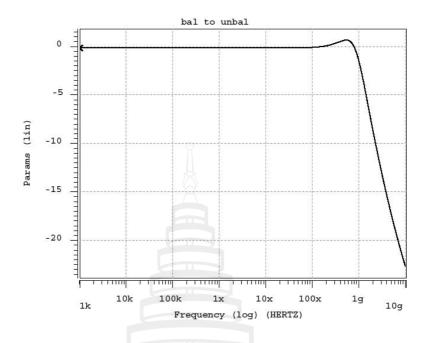

**Figure 4.15** Frequencies Response and dB from  $V_o$  Output of Power Split BALUN, -3dB Bandwidth is 15.7GHz

**Figure 4.16** Frequencies Response of Phase Differential 180 Degree Output from Power Split BALUN with 7.14° of Phase Imbalance at -3dB (15.7GHz)

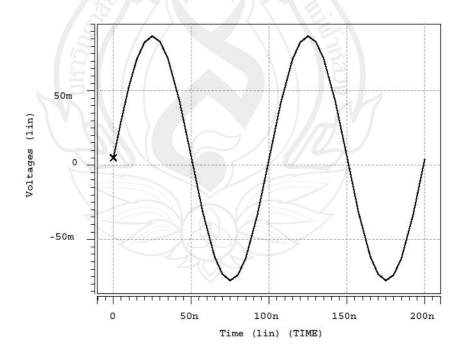

**Figure 4.17** Drifferential Output of Power Split BALUN Transient Analysis for Input 10mV at 2.5GHz

Figure 4.18 Frequencies Response of Input Impedance from Power Split BALUN

**Figure 4.19** Frequencies Response of Positive Output Impedance from Power Split BALUN

Figure 4.20 Frequencies Response of Negative Output Impedance from Power Split BALUN

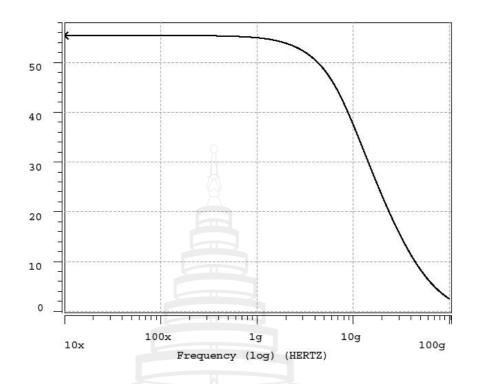

## 4.5 Power Combined BALUN Results

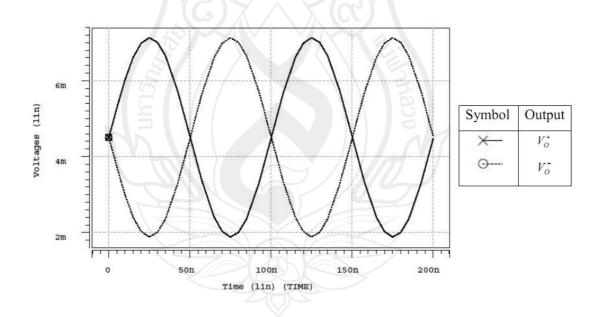

## 4.5.1 Results from 0.35µm SiGe BiCMOS Power Combined BALUN

The output of the power combined BALUN is also simulated with the same simulator and MOSFET model. The biases current are 190  $\mu A$  for both OTAs. The output frequency response is shown in Figure 4.21, and the transient response based on two 10MHz 50mV PP out phase inputs is shown in Figure 4.22.

Figure 4.21 Frequencies Response and dB from  $V_o$  Output of Power Combined BALUN,

-3dB Bandwidth is 1.19 GHz

**Figure 4.22** A Transient Analysis of Combined Output of Power Combined BALUN for 2 Input of 50mV PP which 180° Out Phase at 10 MHz

Figure 4.23 Frequencies Response of Positive Input Impedance from Power Combined BALUN

**Figure 4.24** Frequencies Response of Negative Input Impedance from Power Combined BALUN

**Figure 4.25** Frequencies Response of Output Impedance from Power Combined BALUN

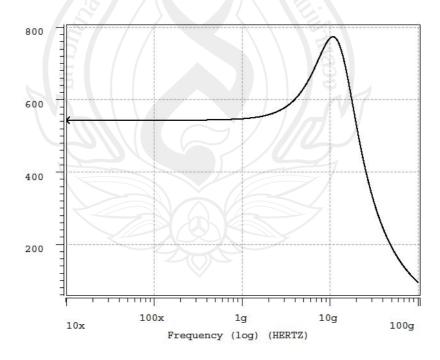

Figure 4.26 CMRR Frequencies Response of Power Combined BALUN

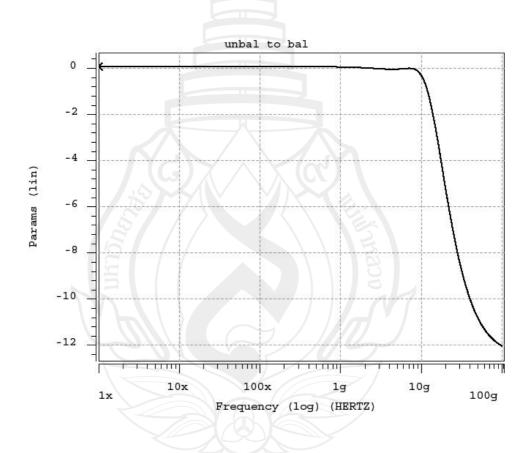

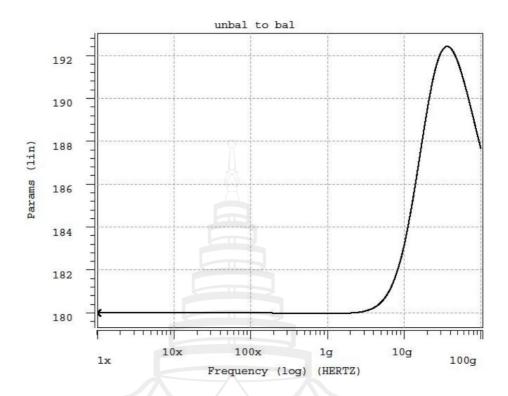

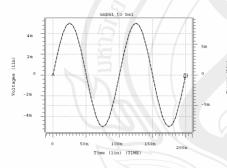

## 4.5.2 Results from IBM 9RF CMOSPower Combined BALUN

The output of the powercombined BALUN is also simulated with the same simulator and MOSFET model as the power split BALUN. The biases current are 190  $\mu A$  for both OTAs. The output frequency response is shown in Figure 4.27 and the transient response based on two 2.5GHz 10mV PP out phase inputs is shown in Figure 4.28, and z-impedance of all input and output portsis showninFigure 4.29, 4.30 and 4.31.

**Figure 4.27** Frequencies Response and dB from  $V_o$  Output of Power Combined BALUN, -3dB Bandwidth is 17.5 GHz

**Figure 4.28** A Transient Analysis of Combined Output of Power Combined BALUN for 2 Inputs of 10mV PP which 180° Out Phase at 2.5GHz

**Figure 4.29** Frequencies Response of Z Impedance from Power Combined BALUN Positive Input

**Figure 4.30** Frequencies Response of Z Impedance from Power Combined BALUN Negative Input

Figure 4.31 Frequencies Response of Z Impedance from Power Combined BALUN

Output

Figure 4.32 Frequencies Response of Power Combined BALUN CMRR

Table 4.3 Compared Current Bias vs gm and Vdd, Vss between 0.35μm Si-Ge Bi-CMOS and 90 nm IBM 9RF CMOS process

| Proc         | eess   | 0.35um Si-Ge Bi-CMOS | 90nm IBM 9RF CMOS |

|--------------|--------|----------------------|-------------------|

| Current bias | 50 μΑ  | 300μS                | 540μS             |

|              | 100 μΑ | 460μS                | 1.04 mS           |

|              | 150 μΑ | 540μS                | 1.44 mS           |

|              | 200 μΑ | 620µS                | 1.8 mS            |

| Vdd          |        | 3.3V                 | 0.5V              |

| Vss          |        | -3.3V                | -0.5V             |

From Table 4.3, comparing the transcoductance in OTA from 0.35  $\mu$ m SiGe BiCMOS and IBM 9RF CMOS with the same reference current bias as 50  $\mu$ A, 100  $\mu$ A, 150  $\mu$ A and 200  $\mu$ A is noted. The 50  $\mu$ A current in 0.35  $\mu$ m Si-Ge Bi-CMOS that

gives 300  $\mu$ S of the transconductanceand the IBM 9RF CMOS that givesup to 450  $\mu$ S have almost been compared twice. When the current bias increases to 100  $\mu$ A, the model of 0.35 $\mu$ m SiGe BiCMOS will give the transconductance of 460 mS, and 1.04 mS for the model of IBM 9RF CMOS. When the current bias increases to 150 $\mu$ A and 200 $\mu$ A, the transconductance of the 0.35 $\mu$ m SiGe BiCMOS increases to 540  $\mu$ S and 620  $\mu$ S respectively and the IBM 9RF CMOS modelincreases two times to 1.44 mS and 1.80 mS, but these two models still use Vdd and Vss at the same rate which is 3.3 V and-3.3 V for the 0.35 $\mu$ m Si-Ge Bi-CMOS, and 0.5 V and-0.5 V for the IBM 9RF CMOS.

**Table 4.4** Compared BALUN Performance between 0.35μm SiGe BiCMOS and 90 nm IBM 9RF CMOS

| Process    | 0.35μm Si-Ge Bi-CMOS           |                                | 90nm IBM 9RF CMOS    |                       |

|------------|--------------------------------|--------------------------------|----------------------|-----------------------|

| Type of    | Power Split                    | Power Combined                 | Power Split          | Power Combined        |

| BALUN      |                                |                                |                      |                       |

| Number of  | 16                             | 8                              | 16                   | 8                     |

| Transistor |                                |                                |                      |                       |

| Bandwidth  | -3dB @ 1GHz                    | -3dB @ 1.19 GHz                | 0-15.7 GHz           | 0- 17.5 GHz           |

| Phase      | 0.02 ° at 100 MHz              | -                              | 7.14° at 15.7 GHz    | -                     |

| imbalance  |                                |                                |                      |                       |

| Z input    | >2 GΩ @ DC                     | >4 GΩ @ DC                     | >10MΩ @ DC           | $>$ 2 M $\Omega$ @ DC |

|            |                                | >4 GΩ @ DC                     |                      | $>$ 2 M $\Omega$ @ DC |

| Z output   | $1.16 \text{ k}\Omega$ between | $1.12 \text{ k}\Omega$ between | $600 \Omega$ between | 540 $\Omega$ between  |

|            | 0- 100 MHz                     | 0-100 MHz                      | 0-1 GHz              | 0- 1 GHz              |

|            | $1.16 \text{ k}\Omega$ between |                                | $600 \Omega$ between |                       |

|            | 0- 100 MHz                     |                                | 0-1 GHz              |                       |

| CMRR       | -                              | 50 dB between                  | -                    | 50 dB between         |

|            |                                | 0- 100 MHz                     |                      | 0- 4 GHz              |

Table 4.4 for the power split and power combined baluns begins with the bandwidth of the power split balun of  $0.35\mu m$  Si-Ge Bi-CMOS which is 1 GHz at point- 3 dB and the power combined balun which is 1.19 GHz. But for IBM 9RF

CMOS- 3 dB, the bandwidth of the power split balun is 15.7 GHz and the power combined balun is 17.5 GHz, which is several times higher than the 0.35µm SiGe BiCMOS. The Z input impedance of the power split balun is greater than 2 G $\Omega$  and the power combined balun isgreater than 4 G $\Omega$ . But for the IBM 9RF CMOS, the power split balun is greater than 10 M $\Omega$  and the power combined positive and negative input is greater than 2 M $\Omega$ . The Z output power split model of the 0.35µm SiGe BiCMOS is greater than 1.16 k $\Omega$  in the range of 0-100 MHz and the power combined model is greater than 1.12 k $\Omega$  in the same frequency.For the IBM 9RF CMOS, the power split balun in the frequency range of 0-1 GHz is 600  $\Omega$  and the power combined balun is 540  $\Omega$ .For the phase imbalance of the 0.35µm Si-Ge Bi-CMOS, the power split balun will be not more than 0.02 degrees at 100 MHz and CMRR up to 50 dB in the same frequency range, but in the case that 90 nm is 15.7 GHz and the imbalance does not exceed 14.7° and the power combinedCMRR with a 90 nm to 50 dB is in the 0-4 GHz.

## **CHAPTER 5**

## **CONCLUSION**

Previously, the passive BALUN such as the transformer BALUN, the wavelength BALUN and RLC BALUN needed large space which varied inversely with frequency and wasdifficult to be tuned or fabricated within system on chip. After active BALUN circuits with a single transistor or differential pair transistor have come, they can decrease the size of the circuit and are easier to be adjusted to fit the required frequency.

However, there are still some limitations to how each type of transistors works based on its characteristics and quality, including passive sessions in the circuit, because it cannot be used in high-frequency range or wide bandwidth. In order to develop the integrated circuit BALUN, a CCCII module is used as its characteristics can make the BALUN used in wider frequency and the impedance adjusted to fit the required frequency. However, the CCCII structure is complicated because there are various types of the transistors. This causes the fabricated procedure on the Bi-CMOS to be more expensive and larger size than the active OTA BALUN. The design based on the OTA simple structure decreases the number of the transistors and reduces the size of the circuit while increasing response frequencies when fabricated on the same model. Thus, this less complicated OTA BALUN should be inexpensive to be fabricated into system on chip. Its performance is summarized below.

## 5.1 Results of the Simulation

5.1.1 The results of the simulationapparently showed that the limitations of the OTA BALUN depend on the characteristics of the fabricated model. When

changing the model from 0.35µm SiGe BiCMOS to 90 nm 9RF CMOS, the frequency response is better with less pressure and higher reliability.

- 5.1.2 The simulation result of the frequency response of the power split BALUN in 0.35µm SiGe BiCMOS is in the range up to 1 GHz frequencies cutoff while, in 90 nm9RF CMOS, the range is up to 15.7 GHz and the phase imbalance is in the recognized level by using the same OTA but different model.

- 5.1.3 For the power combined BALUN, the frequency response is little different in the wider range of 1.19 GHz for the  $0.35\mu m$  SiGe BiCMOS and 17.5 GHz for the 90 nm 9RF CMOS while the CMRR values of both models are higher than 50 dB in low frequency phase.

- 5.1.4 Both power combined and power split BALUNs can be used to adjust eachbias current in the OTA circuit to compensate for the output to fit the required result.

- 5.1.5 The input impedance of both power split and power combined BALUNs is very high, resulting from the characteristics of the MOS transistor model and the differential pair OTA. Thus, no current is transferred from the input directly to the output, which provides the less reflected signal from the input and the regenerated signal to the output. As a result, the characteristics of the s-parameter cannot be directly used to describe a performance of this BALUN.

### 5.2 Limitations

- 5.2.1 The characteristics of the MOS transistor in each fabricated model have different bias currents and voltage limits, causing the limitations of adjusting the bias current, as the BALUN is hardly to be tuned.

- 5.2.2 Another limitation of the OTA BALUN is frequency response on logarithm. The frequency is first shown in horizontal line response and slightly choking effect is shown in the high frequencies before reaching the cutoff frequencies point (-3dB) which makesthe response bandwidth unstable after that point. It is supposed that the effect came from the hidden inductance in each OTA module.

5.2.3 Compared with other BALUNs, the input and output impedance of this BALUN is many times higher (50  $\Omega$  and 75  $\Omega$ ). Thus, this BALUN circuit needs to integrate the matching impedance circuit in order to make the impedance more suitable to be used with other communication circuits.

## 5.3 Future Work

- 5.3.1 Simulate more advanced models such as 65 nm IBM 10RFe CMOS for expanded frequency response. Decrease the size, test the fabricated model for use, and find environmental effectson the circuits reduce the limitations of the OTA BALUN circuit.

- 5.3.2 Improve the structure of the OTA module to increase frequency responses and integrate a part of the matching impedance to input and output.

- 5.3.3 Find solutions to explain the parasitic inductance that causes the choking effect before frequency cutoff (-3dB) in the OTA circuit in order to reduce the effects and make frequency response flat off before cutoff frequencies by using the Monte Carol analysis and the 3 dimensional fabricated simulation.

## REFERENCES

- Baker, R. J. (2010). **CMOS: Circuit design, layout, and simulation** (3rd ed.). New Jersey: John Wiley & Sons.

- Bohr, M. (2002). **Intel's 90 nm technology: Moore's law and more.** N.P.: Intel Developer Forum.

- Burghartz, J. N., Soyeur, M. & Jenkins, K. A. (1996). Integrated RF and microwave components in BiCMOS technology. **IEEE Trans. Electron Devices, 43**(9), 1559-1570.

- Chuang, H. R. & Kuo, L. C. (2003). 3-D FDTD Design Analysis of a 2.4-GHz Polarization-Diversity Printed Dipole Antenna with Integrated Balun and Polarization-Switching Circuit for WLAN and Wireless Communication Applications. **IEEE Transactions on Microwave Theory and Techniques**, 51(2), 374-381.

- Cooke, H. (1971). Microwave transistors theory and design. **Proc. IEEE, 59**(8), 1163-1181.

- Cressler, J. D. & Niu, G. F. (2003). Silicon-germanium heterojunction bipolar transistors. Norwood, MA: Artech House.

- **Euro Practice-IC.** (2012). Retieved August 18, 2012, from http://www.europractice -ic.com/technologies AMS.php?tech\_id=SiGe

- Gnecchi, J. A. G. (2010). Voltage Controlled Current Source (VCCS) for Electrical Impedance Tomography (EIT) measurements in the α and β dispersion frequency ranges. In **Electronics, Robotics and automotive mechanics conference** (pp. 677-681). Cuernavaca, Mexico.

- Godara, B. & Fabre, A. (2007). Impedance-controlled wideband active balun based on current conveyors. **Electronics Letters, 43**(16), 865-867.

- Godara, B. & Fabre, A. (2008). A highly compact active wideband balun with impedance transformation in SiGeBiCMOS. **IEEE Transactions on Microwave Theory and Techniques, 56**(1), 22-30.

- Kelly, S. C., Power, J. A., Oapos & Neill, M. (2003). Optimization of integrated RF varactors on a 0.35 mum BiCMOS technology. In International conference on microelectronic test structures (pp. 94-99). UK.: Institute of Electrical and Electronics Engineers.

- Larson, L. E. (1998). Integrated circuit technology options for RFIC's-present status and future direction. **IEEE J. of Solid State Circuits, 33**(3), 387-399.

- Mecke, J. (2004). **IBM Foundry Offeringsoundry Offerings.** Retrieved August 21, 2012, form http://www.gobookee.com/get\_book.php?u=aHR0cDov L3cyLmNhZGVuY2UuY29tL3doaXRlcGFwZXJzL3dpcmVsZXNzX3NvbH V0aW9uc19zYW5kaWVnb18wMTA2MDUucGRmCklCTSBGb3VuZHJ5IE 9mZmVyaW5ncyAtIENhZGVuY2UgRGVzaWduIFN5c3RlbXM=

- MPS Industries. (n.d.). **Balun transformers.** Retieved August 18, 2012, from http://www.mpsind.com/MPS-pages/MPS-product-pages/balun-transformers. html

- Osamu, O. (ed.). (2007). Compound semiconductor bulk materials and characterizations, Aichi science & technology foundation. Japan: World Scientific.

- Puchner, H. (1996). Advanced process modeling for VLSI technology technical. Vienna: University of Vienna, Faculty of Electrical Engineering.

- Roozbahani, R. G. (2004). BJT-BJT, FET-BJT, and FET-FET. Circuits and Devices Magazine, IEEE, 20(6), 17-22.

- Sittan Udomsom, Paweena Suebsombut, Teevavisit Laohapensaeng & Roungsan Chaisricharoen & Higuchi, K. (2012). "Active tunable nanoscale CMOS BALUN based on operational transconductance amplifier. In **Industrial Electronics and Applications (ICIEA), 2012 7th IEEE Conference** (pp.1738-1741). Singapore: Industrial Electronics and Applications.

- Sittan Udomsom, Teevavisit Laohapensaeng & Roungsan Chaisricharoen. (2012).

Tunable active CMOS balun based on operational transconductance amplifier.

In International Conference on Embedded Systems and Intelligent

Technology (ICESIT2012) (pp. 195-198). Nara, Japan: Engineering Science

Society, The Institute of Electronics, Information and Communication

Engineers (IEICE-ESS).

- TORKI, K. (2011). CMP. In Workshop on Microelectronics beyond the GHz, Clermont-Ferrand. Grenoble, France.

- Wendell, R. J. (n.d.). **WBØJNR: My amateur radio station.** Retieved August 18, 2012, from http://www.rogerwendell.com/mystation.html

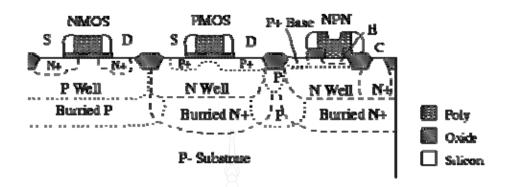

## APPENDIX A

## Austria Microsystem SiGe BiCMOS 0.35 µm

The concept of combining silicon (Si) and germanium (Ge) into an alloy for use in transistor engineering is an old one (Burghartz, Soyeur, Jenkins, 1996). However, because of difficulties in growing lattice-matched SiGe alloy on Si (Osamu, editor, 2007). this concept is reduced to practical reality only in the last 15 years. SiGe HBT (Cressler & Niu, 2003) technology was originally developed at IBM for the high-end computing market, that effort, however, failed to CMOS, primarily because of its high power consumption.

In the early 1990s, IBM refocused SiGe program for developing in communications market. Interestingly, for RF communications circuits, SiGe HBT consumes much less power than CMOS to achieve the same level of performance. Since then, significant progress has been made. SiGe technology is being developed and applied around the world, and then is in the product roadmap of every major telecommunication company. Applications range from wired and wireless communications circuits, to disk storages, to high speed high bandwidth instrumentation. The use of discrete SiGe HBTs and amplifiers in wireless devices is common place. Integrated SiGe chips can be found in GSM and CDMA wireless handsets and base stations, wireless LAN chipsets, and high-speed 10-40 Gb/s synchronous optical network (SONET) transceivers.

From Puchner, H. (1996). Advanced process modeling for VLSI technology technical. Vienna: University of Vienna, Faculty of Electrical Engineering.

Figure A1 Structure of NMOS, PMOS and Transistor on SiGe BiCMOS Process

**Table A1** Characteristics of 0.35um SiGe BiCMOS

| Process Name            | unit           | S35D3M2      | S35D4M2      | S35D4M5       |

|-------------------------|----------------|--------------|--------------|---------------|

| Process Type            | /-/            | SiGe BiCMOS  | SiGe BiCMOS  | SiGe BiCMOS   |

| Drawn MOS Channel       | μm             | 0.35         | 0.35         | 0.35          |

| Length, Drawn Emitter   | μm             | 0.4          | 0.4          | 0.4           |

| Width                   |                |              |              |               |

| Operating Voltage       | V              | 2.5-3.6      | 2.5-3.6      | 2.5-3.6 / 5.5 |

| CMOS                    |                |              |              |               |

| Number of Metal Layers  | <u> </u>       | 3            | 4            | 4             |

| Number of Poly Layers   |                | 4            | 4            | 4             |

| Substrate Type          | 4              | P            | P            | P             |

| Diffusion Pitch         | μm             | 0.9          | 0.9          | 0.9           |

| Metal1/2/3 Pitch        | μm             | 0.95/1.1/1.2 | 0.95/1.1/1.2 | 0.95/1.1/1.2  |

| Poly1 Pitch             | μm             | 0.8          | 0.8          | 0.8           |

| Thick Metal 4 pitch     | μm             | -            | 4.5          | 4.5           |

| High Resistive Poly     | kOhm/#         | -            | -            | 1.2           |

| Poly1 / Poly2 Precision | $fF/\mu m^{2}$ | 0.9          | 0.9          | 0.9           |

| Caps                    |                |              |              |               |

Table A1 (Continued)

| <b>Process Name</b> | unit          | S35D3M2 | S35D4M2 | S35D4M5 |

|---------------------|---------------|---------|---------|---------|

| Metal 2 / Metal 3   | fF/μm²        | 1.25    | 1.25    | 1.25    |

| Precision Caps      |               |         |         |         |

| N/PMOS Active       | μm            | 0.3/0.3 | 0.3/0.3 | 0.3/0.3 |

| Channel Length      |               |         |         |         |

| N/PMOS Saturation   | $\mu A/\mu m$ | 540/240 | 540/240 | 540/240 |

| Current             |               |         |         |         |

| Gain                | -             | 160     | 160     | 160     |

| Early Voltage VAF   | V             | 100     | 100     | 100     |

| HS-HBT: BVceo       | V             | 2.7     | 2.7     | 2.7     |

| ft / fmax           | GHz           | 60 / 70 | 60 / 70 | 60 / 70 |

| HV-HBT: BVceo       | V             |         | -       | 5.5     |

| ft / fmax           | GHz           |         | -       | 30 / 50 |

From TORKI, K. (2011). CMP. In Workshop on Microelectronics beyond the GHz, Clermont-Ferrand. Grenoble, France.

## **APPENDIX B**

# Tunable Active CMOS Balun Based on Operational Transconductance Amplifier

Sittan Udomsom,

Teeravisit Laohapensaeng and

Roungsan Chaisricharoen

School of Information Technology Mae Fah Luang University

Chiang Rai, Thailand

hs5xkp@gmail.com

Abstract-In modern communication systems, the signal splitter called BALUN (BALance to UNbalance) is required to interface a single ended device with a differential ended device. Most active BALUN use passive elements which cannot be tuned and require a large area on the integrated circuit. Though there is the controllable BALUN based on BiCMOS CCCII, the implemented circuit is quite large in transistor count and the cost of BiCMOS is very expensive. In this work, a new active BALUN based on CMOS OTA is proposed. By adjusting the transconductance of the composed OTAs, the characteristics of BALUN can be tuned electronically. Normally the size of the OTA is half of the size of the CCCII in transistor count. Therefore, the size of proposed structure is theoretically half of the CCCII counterpart. The design structure is simulated in the HSPICE based on the AMS  $0.35\mu$  CMOS process. Demonstrated in simulation results, the proposed structure can be a fair alternative in BALUN design due to adequate compatibility of BALUN characteristics such as power splitting and inverse phase.

Keywords-component; Operational Transconductance Amplifier, Active BALUN, CMOS

### I. INTRODUCTION

Nowadays, most transceivers are composed of both single ended (SE) and differential ended (DE) components. Therefore, a converter circuit called BALance to UNbalance (BALUN) converter is usually needed. Most BALUN designs are based on passive components [1], BJT [2], and BiCMOS[3]. Though these designs work well on their own, most transceivers are favored to be fabricated based only on complementary MOS (CMOS) to be placed among various digital functions. In addition, ability in tuning is also a good option in a BALUN [4, 7] to cover error in gain matching that is likely to occur with quite high probability in practical systems.

Interestingly, the operational transconductance amplifier (OTA) simulating voltage-controlled current source (VCCS) [5] is one of the favorite active analogue devices because the transconducatance can be tuned electronically via bias current. Therefore, key properties of its applications can be easily